티스토리 뷰

https://18electronics.tistory.com/22

[VLSI] 디지털 회로의 Power(1) - 18EE

현재 디지털 회로를 구성할 때 중요한 trade off 중 하나는 speed와 power이다. 딜레이에 관한 내용은 정리해놓았다. https://18electronics.tistory.com/19 [VLSI] 디지털 회로의 Delay(1) - 18EE CMOS 특성 디지털 회로

18electronics.tistory.com

cf) fsw : switching activity factor를 고려한 transition frequency

| 개선점 | 방법 및 trade off |

| Lower VDD | - 가장 효과가 좋은 방법이다. - Speed와 trade off 관계이므로 쉽게 줄일 수 없다. - Multiple VDD사용 |

| Lower CL | - Tr size reduction - Shorter metal(compact layout) |

| Lower a(switching activity factor) | - architecture 변경 - Frequency scailing - Clock gating |

| Lower leakage | - High Vth - Speed와 trade off 관계이므로 Vth를 쉽게 늘릴 수 없다. - Power gating |

cf) frequency scailing을 할 때는 voltage도 같이 scailing한다.(lower VDD -> lower frequency)

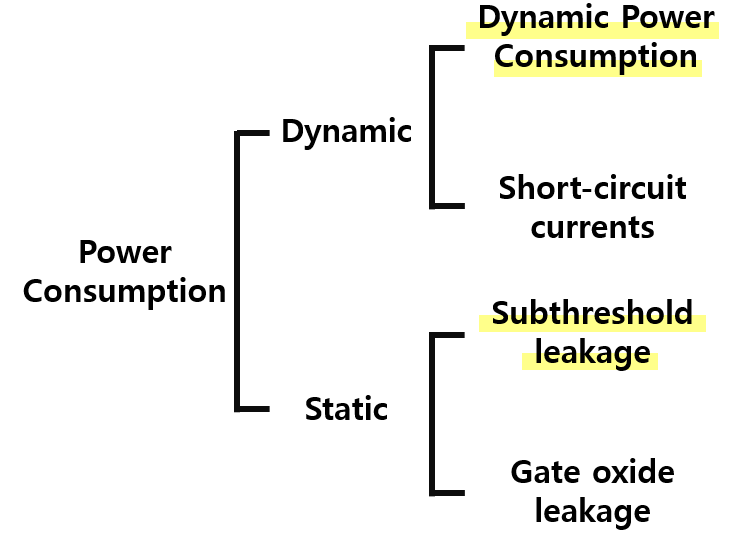

Power 소모의 원인과 그 해결법을 정리해보면 다음과 같다.

- Dynamic power consumption : lower VDD, lower a

- Subthreshold leakage : High Vth

크게 Dynamic power consumption을 개선하는 방법과 Subthreshold leakage를 개선하는 방법을 두번에 걸쳐 소개하겠다.

소개

| System level(lower VDD) | - Multiple VDD - Dynamic Power Management(DPM) |

| Dynamic(lower a) | - Clock gating - Data gating |

| Static(high Vth) | - State Assignment - Power Gating - Dual Vth Assignment - Body biasing |

Dynamic : 회로가 동작하며 low power technique이 적용된다.

ex) Clock gating : gating이 될 수도 있고 안될 수도 있고

Static : 회로가 동작하기 전에 미리 low power technique이 적용된다.

Dynamic power consumption 개선

Dynamic power를 개선하기위해서는

'VDD를 낮추거나 transition 빈도를 낮추면 된다.'

System level (lower VDD)

VDD를 낮춰 Dynamic power를 개선하는 방법이다.

1. Multiple VDD

전체 system을 domain별로 나눠

느린 domain : 낮은 VDD

빠른 domain : 높은 VDD

를 공급하는 방법

domain간 전압이 다르므로 level shifter가 필요하고 중요하다. level shifter는 LOW to HIGH shifter가 중요하다. 다음은 level shifter의 예시들이다.

cf) HIGH to LOW는 timing만 잘 맞춰주면 된다.

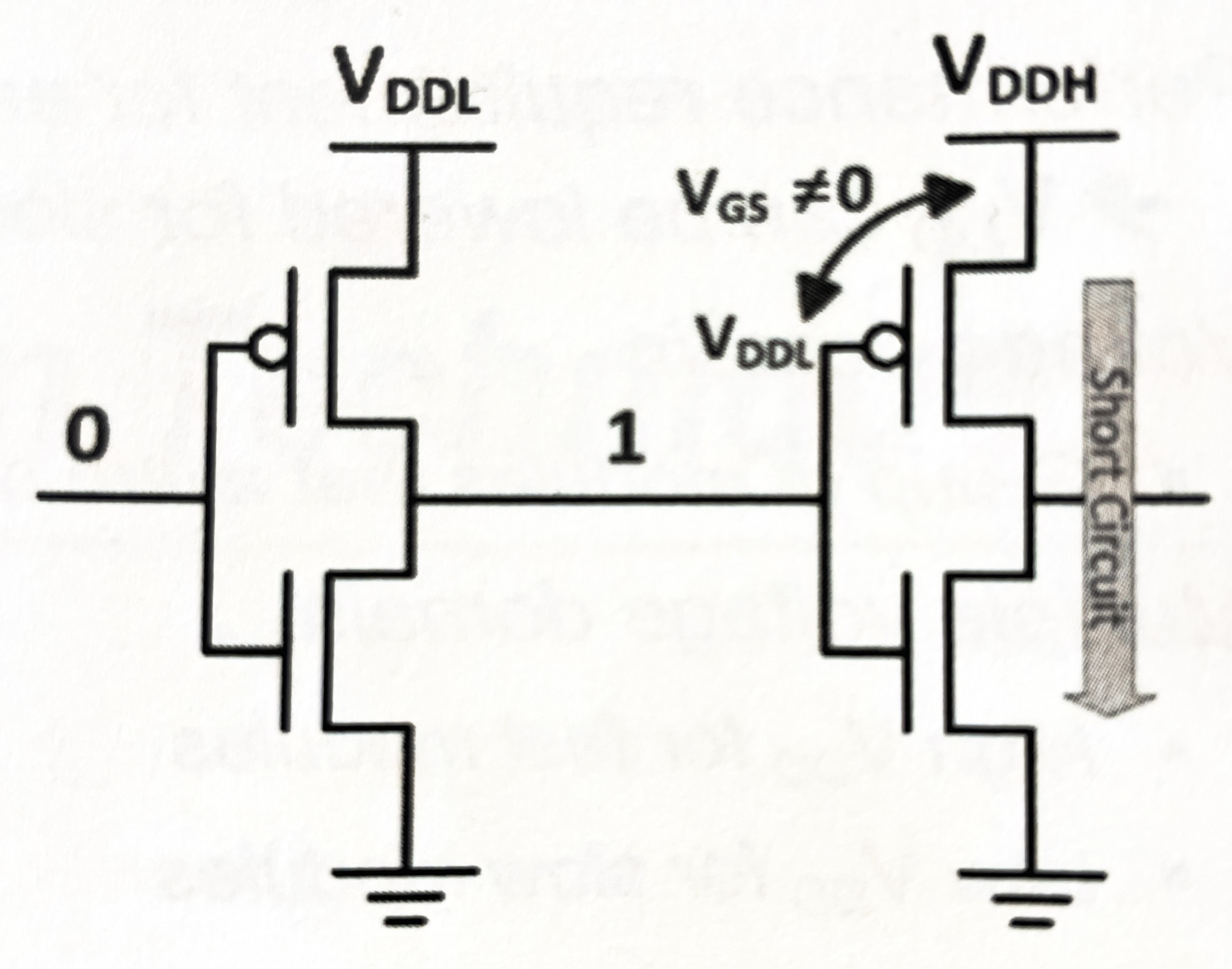

1. Standard high to low level shifter

2개의 inverter를 사용하는 방법이다. 하지만 뒷단의 VGS=VDDH-VDDL이므로 PMOS가 완전히 OFF되지않아 short current가 발생해서 계속 흐른다. 따라서 큰 전력소모가 나므로 사용하지 않는다.

2. Conventional DCVS

VDDH와 VDDL 차이가 많이 나지 않을 때 사용한다.

3. Passgate level shifter

M4를 equalizer처럼 사용해서 level shifter를 구성한 것이다. low power, less TR의 장점이 있다.

Multiple VDD의 이슈들이 있다.

| Partitioning | - domain을 나누기 힘들다. - logical하게 나눌것인가? physical하게 나눌것인가? |

| Voltage/Frequency | - domain마다 어떤 VDD와 frequency를 사용할 것인가? - VDD가 달라 전체 system의 timing을 맞추기 힘들 수 있다. |

| Level shifter | - 추가 회로 필요 - delay 증가 |

| Physical Design | - PnR작업시 VDD rail을 고려해야한다. |

2. Dynamic Power Management (DPM)

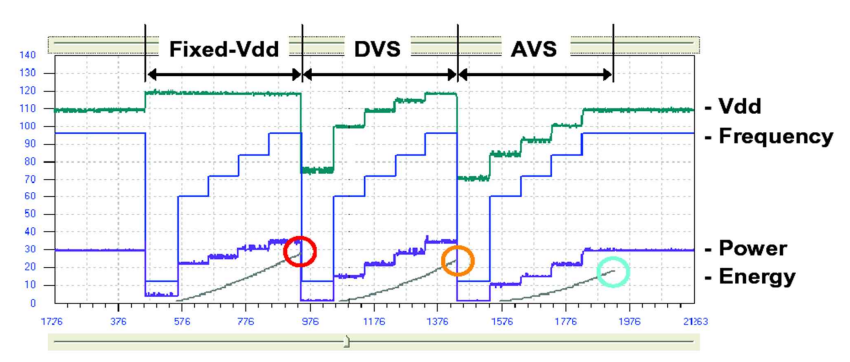

'늦게 끝내도 되는 일은 낮은 VDD를 사용하여 느리게 끝내고 전력소모를 줄이자.'

기존 energy의 36%만 사용한 것을 볼 수있다.

다음은 DPM의 종류이다.

| DVS (Dynamic voltage scailing) | Voltage만 바꾸기 |

| DFS (Dynamic frequency scailing) | Frequency만 바꾸기 |

| DVFS (Dynamic voltage and frequency) | Voltage, frequency 둘 다 바꾸기 |

| AVFS (Adaptive voltage and frequency scailing) | 상황에 맞게 적응하여 바꿈 |

1. Dynamic vs Adaptive

Dynamic : 각 mode마다 정해진 voltage가 정해져있어서 mode를 바꾸면서 동작한다.

Adaptive : 현재 상황을 계속 monitoring하면서 그에 맞게 전압과 frequency를 조정한다.

DVFS는 VDD가 mode에 맞도록 바뀌기때문에 급격하게 VDD, frequency가 바뀌는 모습을 볼 수 있다.

AVFS는 현재 상황을 monitoring하며 VDD를 바꾸기때문에 점진적으로 VDD, frequency를 바꾼다.

AVFS를 사용하는 이유

- DVFS는 각 mode에 맞는 VDD를 가지고있다. game mode일 때 온도가 높으면 game이 꺼진다. 하지만 AVS는 상황에 맞게 VDD와 frequency를 scailing할 수 있기때문에 꺼지는 것을 방지할 수 있다.

- DVFS는 칩이 완성되었을 때 각 domain별로 예상했던 빠르기와 VDD가 아닐 수도 있다. AVFS는 오차가 있다고 하더라도 적응형이기 때문에 유연하게 대처할 수 있다.

AVFS의 단점

- monitoring하는 추가적인 회로가 필요하다.

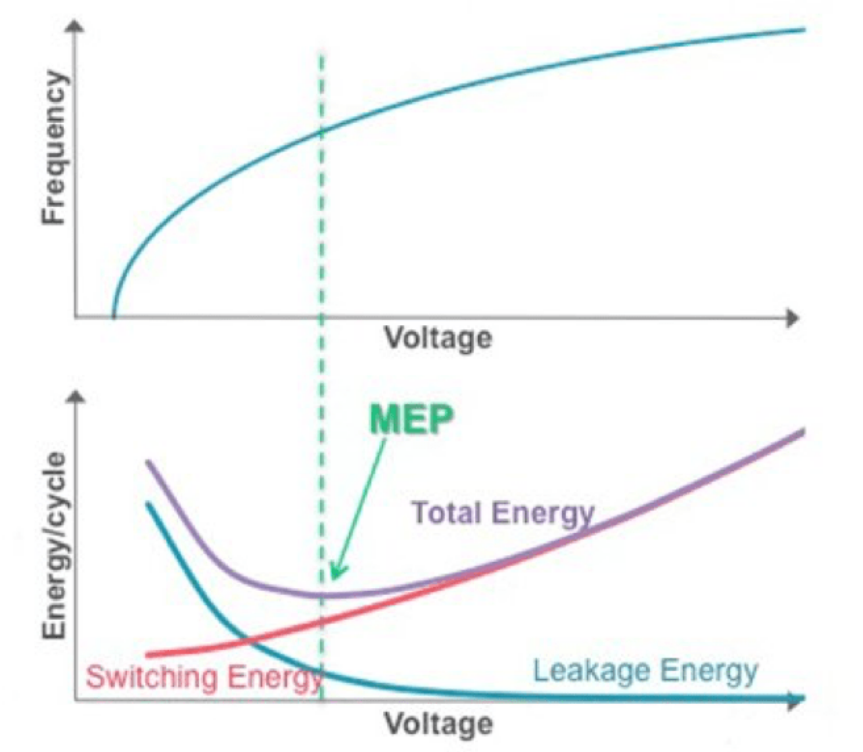

3. Near threshold voltage(NTV)

VDD를 계속 낮추면 Dynamic energy를 줄일 수 있다. 하지만 특점 전압 이하로 내려가면 Leakage energy가 증가한다. 즉, energy의 최소점이 존재하고 이 점이 Vth 주변에 있기때문에 Near threshold voltage라고 부른다. VDD를 줄여 energy를 줄였으나 역시 frequency는 감소한다. 따라서 speed보다는 전력이 극도로 중요한 곳에 사용된다.

ex) medical device(하루에 한번 동작, 10년 동작), sensor등

Logic/Circuit level (lower a)

Switcing을 줄여 Dynamic power를 줄일 수 있다.

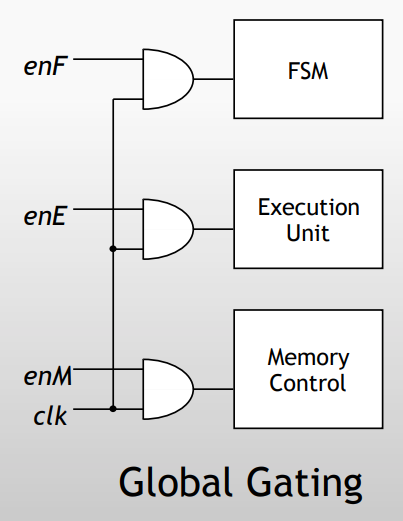

1. Clock gating

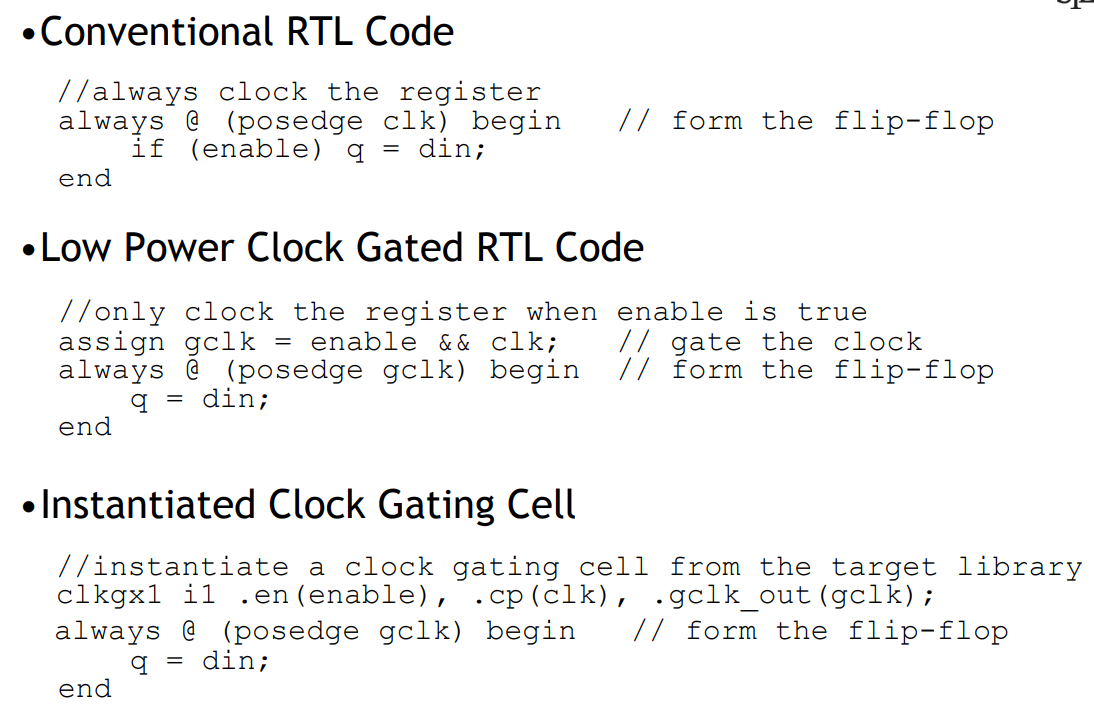

1. DFF clock gating

Clock power도 무시하지 못한다. clock막아서 ouput이 바뀌지 않도록 하는 것이 clock gating이다.

|

|

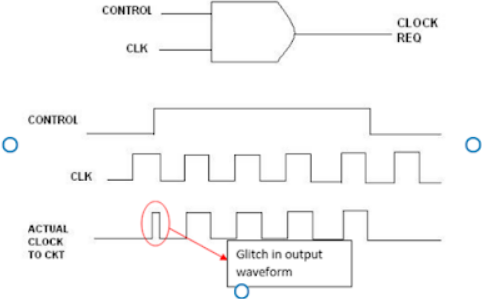

2. Glitch-free clock gating

cf) glitch : 원치않는 spike가 발생하는 것

지연이 일어나면 glitch문제가 발생할 수 있다.

DFF clock gating과의 차이는 always문 안을 보면 알 수 있다.

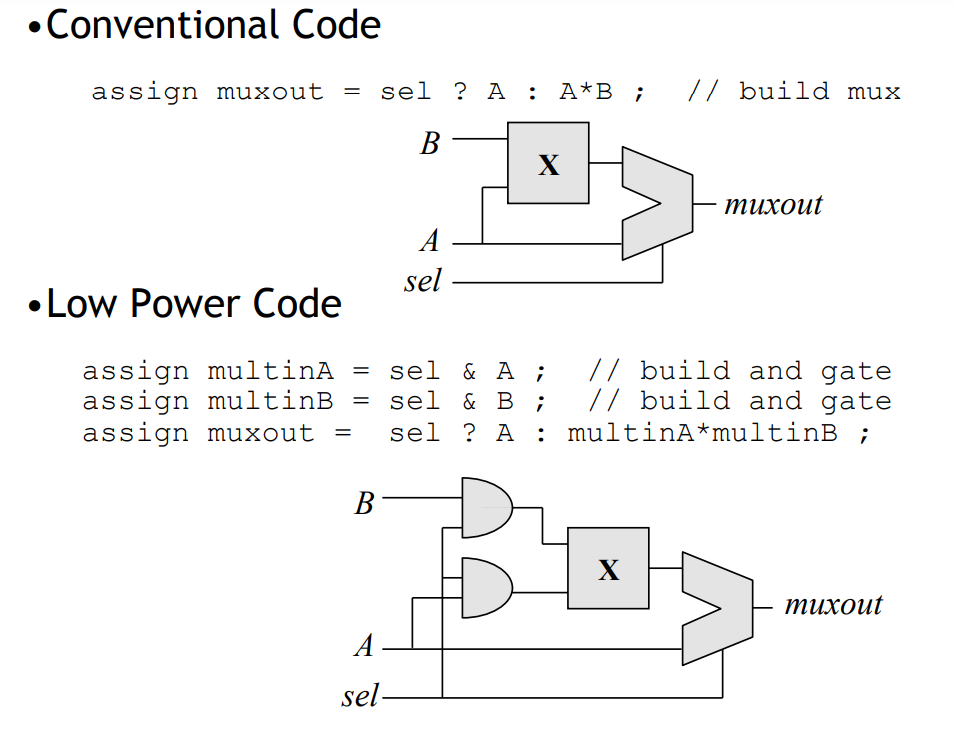

2. Data gating

combination logic의 input을 막는 것이다.

참고자료

http://contents.kocw.or.kr/KOCW/document/2014/sungkyunkwan/hantaehee1/3.pdf

https://semiengineering.com/near-threshold-computing-gets-a-boost/

Near-Threshold Computing Gets A Boost

Why many leading-edge designs are beginning to look like near-threshold designs.

semiengineering.com

https://classes.engineering.wustl.edu/ese461/Lecture/week12b.pdf

'이론 > VLSI' 카테고리의 다른 글

| [VLSI] 디지털 회로의 Power(3) - 18EE (0) | 2023.08.02 |

|---|---|

| [VLSI] 디지털 회로의 Power(1) - 18EE (0) | 2023.07.31 |

| [VLSI] 디지털 회로의 Delay(2) - 18EE (0) | 2023.07.30 |

| [VLSI] 디지털 회로의 Delay(1) - 18EE (0) | 2023.07.30 |

- Total

- Today

- Yesterday

- MTCMOS

- dynamic power

- clock gating

- level shifter

- VLSI power

- DVFS

- 굿노트 mp3파일 추출

- 굿노트 내보내기

- vlsi

- data gating

- VLSI dynamic power consumption

- 굿노트 mp3 내보내기

- VLSI 전력소모

- VTCMOS

- switching power

- ALU

- 굿노트 녹음파일

- CPU

- 4bit CPU

- Stack effect

- Verilog

- acc

- Control Unit

- power gating

- delay

- mp3파일 추출

- static power

- 4bit

- leakage

- CMOS power

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |